# Sensor signal processing using high-level synthesis with a layered architecture

# Dr.HENRY

Dept. of Electronics & Communication Engg, Christu Jyothi Institute of Technology & Science, Jangaon, Telangana, India. hari.cjit@gmail.com

# Dr.JULIE

Dept. of Electronics & Communication Engg, Christu Jyothi Institute of Technology & Science, Jangaon, Telangana, India. ankireddyvnkumar@gmail.com

## **ABSTRACT**

This work describes a newly established design framework with the layered architecture of processing elements exploiting high-level synthesis and its evaluation results. The design framework was developed for intelligent sensor nodes of Internet of Things (IoT) applications that collaborate with cloud systems, in which small footprint and low power consumption were major concerns. The design framework consists of four layered structure of processing element architecture with the extended database management function of a high-level synthesis tool. We investigated the dependencies of resource consumption on the granularity of coarse grained function definitions using the extended database management function of Cyber Workbench (CWB). The evaluation results showed that small footprint was achieved especially with dynamically reconfigurable technique.

**Key words**—high-level synthesis, behavioral synthesis, microcontroller, field programmable gate array, dynamically reconfigurable processor, Internet of Things, device computing

# INTRODUCTION

Sensor nodes are important elements of Internet of Things(IoT) applications, whereas the transmission capacity of existing network channels is limited between sensors and cloud systems. In consequence, reducing data volume is necessary by accommodating device computing functions within sensor nodes to transmit sufficient data through existing networks. Small footprints and low power consumption are demanded for processing elements (PEs) within sensor nodes.

Field programmable gate arrays (FPGAs) are alternatives of microcontroller units (MCUs) to reduce the size of footprints, whereas the inefficiency of placement and routing (P&R) using configurable logic blocks (CLBs) and look-up tables (LUTs) with switches, together with associated configuration memories, is pointed out [1]. High level synthesis is used for the design of FPGAs to enable global optimization and to compensate for the limitation of P&R.

We propose a new design framework with four-layer architecture to design embedded PEs in sensing devices of IoT applications using the database management function of a highlevel synthesis tool. It exploits the repetitive high-level synthesis process. Macro blocks synthesized through highlevel/behavioral synthesis are registered in a database before the system level synthesis, and the information in the database used for the optimization of resource consumption through the system level synthesis. We investigated the dependencies of resource consumption on the granularity of coarse grained function definitions using the extended database management function of Cyber Workbench (CWB) [2]. The evaluation results show that small footprint was achieved especially with dynamically reconfigurable technique.

# I. RELATED WORK AND PROBLEM FORMULATION

Input sequences for embedded systems come from real world, and the input data for PEs are given serially. Backward data access is not necessary. Wire-rate processing using FPGAs is suitable for adding processing functions with minimum additional footprints.

Various optimization techniques of filtering functions for sensing images were summarized and proposed [3, 4, 5]. P&R as area-optimal mapping was also mentioned, whereas these improvements were based on the optimization of scheduling and did not exploit the functional representation of circuitry definitions used in high-level synthesis. Design re-use of macro blocks by considering the functional representations of macro blocks used in high level synthesis was proposed to optimize P&R process [6]. The reported method is applied to the layout process

after logic synthesis. Code Generation optimization using high-level synthesis was reported [7], whereas high-level synthesis is used for the optimization of streaming pipelines. If the functional representations of macro blocks are exploited in high-level/behavioral synthesis step, more chances of optimization can be found.

Dynamically reconfigurable processors (DRPs) using highlevel synthesis were proposed [8, 9, 10] to improve the efficiency, whereas the inefficiency of fixed mesh pointed out in [1] still remains. Fixed bit widths of data paths, elementary blocks and switch matrices aiming at mass production of the devices was one example of the inefficiency. Sensors used in IoT applications have various data interfaces, such as 8, 12, 14, or 16 bits. Predefined data path between arrays of arithmetic logic units (ALUs) prevents behavioral synthesis tools from the optimization of layout size and the reduction in power consumption. Therefore, optimized ALUs and flexible data paths are required to embed processors in sensor units.

We identified two issues those were missing in the conventional optimization methodologies. The first issue is the exploitation of the functional representation of macro blocks. The use of macro definitions in high-level synthesis using functional representations enables additional global optimization. The second issue is eliminating constraint found in conventional mesh type FPGAs and DRPs for the wire rate signal processings. Bit width of ALUs and data paths should be optimized for specific sensors while maintaining the merit of DRPs.

# II. THE ARCHITECTURE OF PROCESSING ELEMENTS

We established a new design framework to solve issues described in the preceding section by exploiting the binding process of high-level/behavioral synthesis.

# A. Layered architecture

The purpose of the conventional high-level synthesis tools is to generate finite state machines with data paths (FSMDs). We refer to FSMD as fine grained layer. We expanded the scope of high-level synthesis to coarse grained layer to exploit the functional representations of circuitries. ALUs in coarse grained layer are defined by the functional representations of high level programming languages. We also added switches as bypass connection layer for the scope of high-level synthesis intentionally. Implicit as-built meshes of switches put constraints on high-level synthesis. We allowed some PEs to be just bypass switches to remove the meshes. Communications between the PEs are limited between adjacent PEs, whereas we found no limitations for sensor applications with the limited communication paths.

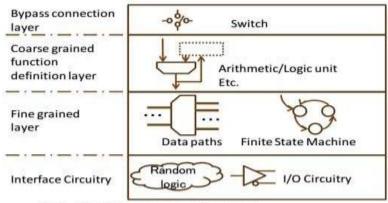

Fig. 1. The proposed four-layered structure

The four-layered structure is shown in Fig. 1. The layers consist of I/O circuitry, fine grained layer, coarse grained function definition layer and bypass connection layer, where they are listed from the bottom layer to the top layer, respectively. The following explains these layers.

I/O circuitry is implemented with random logic gates and mixed signal I/O circuitries. They are connected to the fine grained blocks in the above layer. The fine grained layer mainly consists of finite state machines and data paths. They are replaceable to follow the context described by high level languages. The coarse grained function definition layer is located on the fine grained layer. Optimized ALUs for a certain application are defined in this layer. An operation primitive defined in the layer corresponds to an operation code (opcode) of a conventional MCU, whereas it does not have to be standardized for overmany applications. As for the topmost bypass connection layer, simple bypass switch images can be specified over coarse grained blocks. The connections between inputs and outputs of PEs are configurable with the bypass switches.

# B. The design flow

The following six steps compose the design flow of the design framework to design a PE through layered scheme.

- [Step 1]: Describe a system in high-level language.

- [Step 2]: Define coarse grained operations. Typical dedicated functions for sensor signals are signal compensation, feature point identification for image recognition, and image compression in addition to basic arithmetic operations. The defined coarse grained operations are exploited in high-level synthesis and behavioral synthesis process.

- [Step 3]: Generate source codes written in hardware description language (HDL) through behavioral synthesis. The hard macros defined and implemented in the step 2 are exploited for generating circuitries by the functions of CWB.

- [Step 4]: This step is identical to conventional logic synthesis.

- [Step 5]: This step is identical to conventional layout design.

- [Step 6]: The verification and validation step include back annotation based on the result of delay analysis.

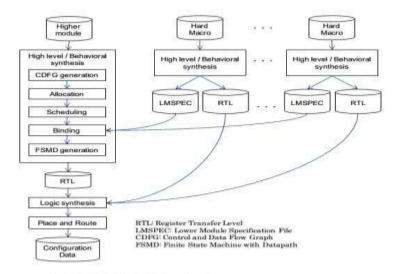

Fig. 2. Modified high-level synthesis process

We used a data base management function of CWB to exploit the definitions of operations in the coarse grained layer during the behavioral synthesis to treat a function as an operator. The operations can be implemented as hard macros by using custom ASIC design tools and/or LUTs of FPGAs. The operator definitions were exploited on the step 3 as macro blocks. They are registered in a database of CWB as shown in Fig. 2. Once macro blocks are registered in a database, CWB can use the macro blocks during the binding process of high-level synthesis automatically to reduce layout area size. The binding process of high-level synthesis is regarded as NP-hard and

heuristic approach was often employed. The design flow enables the automation of binding process instead of the heuristic approach.

# C. The typical design of a processing element

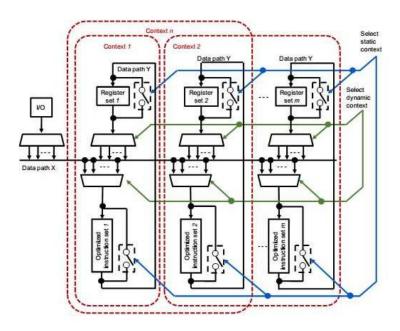

Two types of context were identified with reference to semantics or lambda calculus of functional representations to define ALUs in coarse grained function definition layer. One is a configurable static context often mentioned as stored information in a file, and the other is a dynamic context as stored information in heap registers as shown in Fig. 3. The static contexts of an application are expressed with finite state machines and data paths implemented by n sets of hardware circuitry of PEs. The dynamic contexts of an application are specified as m sets of registers and instructions. The instruction sets are optimized for an application, and each optimized instruction set can be shared among some dynamic contexts.

We implemented a specific C-language comment description /\* Cyber func = operator \*/ for defining dynamic and static contexts, which are the sets of pairs of registers and optimized instruction sets. The pair of a register set and an instruction set can be shared among dynamic contexts using another specific C-language comment description as /\* Cyber share\_name =NAME \*/. NAME is an arbitrary designation. The binding process of high-level behavioral synthesis can be controlled by these descriptions to exploit the functional representations defined in a high level programming language.

# III. EVALUATIONS AND RESULTS

We evaluated the design framework using convolution operations, those are often used for sensor applications, with following three conditions. The matrix functions of the filters are similar and the difference is the parameters of 3 x 3 matrices. We could evaluate the layout area size reduction results by using an FPGA, Xilinx XC7A200T FPGA, although the design framework was established aiming at improving ASIC design at first.

- A) Defining a convolution function as one operator,

- B) Implementing ALUs with basic operations, i.e. plus, minus, multiply, divide, and comparison operations, using dynamically reconfiguration technique designated as Flexible Reliability Reconfigurable Array (FRRA) in [11],

- C) Elaborating whole design with FPGA libraries without operator definitions and a function definition database.

We implemented a Laplacian filter with above three conditions in one case and the cascaded operations with a Gaussian filter and a Laplacian filter in another case. These filters are often used for image processing, and the cascaded operation is useful for robust edge detection. Operator definitions and resource sharing are specified for the condition A) as shown in Fig. 4. Two filter functions were registered in the database by specifying CWB using the annotation "/\* Cyber func = operator \*/", and they were used repeatedly as independent operators in the high-level and behavioral synthesis processes. The matrix functions were not registered independently in the database in the other conditions. The operator '+' can be shared between Laplacian\_filter function and Gaussian\_filter function by the annotation "/\* Cyber sharename=ALU1\*/". This annotation is a direction for CWB to assign the same operator for '+' in Laplacian\_filter function and in Gaussian\_filter function. If these functions are processed sequentially both '+' operation can be carried out by the same operator. On the other hand, if each '+' operator works in parallel and cannot be shared, a suffix is added to the name ALU for independent identification and two operators are synthesized. This sharing status is decided by CWB automatically through the process of control and data flow analysis. Designers don't have to care about whether two functions are processed sequentially or in parallel, and they can concentrate on the analysis of the sharing possibility of operators using the annotation "/\* Cyber func = ... \*/".

ISSN NO: 2249-3034

Fig. 3. The context implementation of a PE: On/Off state of switches are logical images.

```

/* Cyber func = operator */

unsigned short Laplacian_filter ( unsigned short pixel_buffer[PEL]) {

short temp;

pixel_buffer_s[9]; /* 3 x 3 convolution filter element */

...

temp = pixel_buffer_s[Num0] + /* Cyber share_name=ALU1 */

pixle_buffer_s[Num1];

...

}

/* Cyber func = operator */

unsigned short Gaussian_filter ( unsigned short pixel_buffer[PEL]) {

short temp;

pixel_buffer_s[9]; /* 3 x 3 convolution filter element */

...

temp = pixel_buffer_s[Num0] + /* Cyber share_name=ALU1 */

pixle_buffer_s[Num1];

...

}

```

Fig. 4. Operator definitions and operator sharing for condition A)

# V. CONCLUSION

We developed a novel design framework to reduce the footprints of programmable functions of sensing devices for IoT applications. The design framework consists of four layered structure of processing element architecture and the extended database management function of a high-level synthesis tool to exploit functional representations in high-level programming languages.

We investigated the dependencies of layout size on the granularity of filtering function definitions using the extended database management function of CWB. We succeeded in automatic layout size reduction of an FPGA through the binding process of CWB by exploiting the functional representations in C language. It was realized by using annotations in program source code descriptions to show the information of resource sharing possibilities for high-level synthesis. This was achieved through step 2 and 3 of the design framework. We found that function definitions using dynamically reconfigurable processing technique is also effective to reduce layout size.

The layout size reduction is useful to embed a PE into a sensing device and to provide device computing capabilities with a sensing device. We also reported the power consumption reduction by adopting the design framework on a NanoBridge FPGA [12].

# REFERENCES

- [1] R. Hartenstein, "The Microprocessor Is No Longer General Purpose: Why Future Reconfigurable Platforms Will win," in *Proc. Second Annual IEEE Intl. Conf. on Innovative Systems in Silicon*, 1997, pp. 2-12.

- [2] K.Wakabayashi, "CyberWorkBench: Integrated design environment\ based on C-based behavior synthesis and verification," in *Proc. IEEE VLSI-TSA Intl. Symposium*, 2005, pp. 173-176.

- [3] R. Zhao, M. Tan, S. Dai, Z. Zhang, "Area-efficient pipelining for FPGAtargeted high-level synthesis," 2015 52nd ACM/EDAC/IEEE Design Automation Conference (DAC)s, 2015, pp. 1-6.

- [4] F. Wang, G. Wang, R. Wang, X. Huang, "FPGA implementation of Laplacian of Gaussian edge detection algorithm," *Advanced Materials Research*, vol. 282-283, 2011, pp. 157-160.

- [5] L. Chen, "Fast Generation of Gaussian and Laplacian Image Pyramids Using an FPGA-based Custom Computing Platform," Master degree thesis, Virginia Polytechnic Institute and State Univ., 1994.

- [6] M. Gort, J. Anderson, "Design re-use for compile time reduction in FPGA high-level synthesis flows," *2014 Intl Conf. on Field-Programmable Technology (FPT)*, 2014, pp. 4-11.

- [7] M. Schmid, O. Reiche, C. Schmitt, F, Hannig, J. Teich, "Code Generation for High-Level Synthesis of Multiresolution Applications of FPGA," in *Proc. of FSP2014*, 2014, pp. 21-26.

- [8] M. Meribout and M. Motomura, "A Combined Approach to High-Level Synthesis for Dynamically Reconfigurable Systems," *IEEE Trans. On Computers*, vol. 53, no. 12, 2004, pp. 1508-1522.

- [9] T. Toi, N. Nakamura, Y. Kato, T. Awashima and K. Wakabayashi, "HighLevel Synthesis Challenges and Solutions for a Dynamically Reconfigurable Processor," in 2006 IEEE/ACM Intl. Conf. Computer Aided Design, 2006, pp. 702-708.

- [10] Y. Hasegawa, S.Tsutsumi, V.Tanbunheng, T.Nakamura, T.Nisimura, and H.Amano, "Design Methodology and Trade-offs Analysis for Parameterized Dynamically Reconfigurable Processor Arrays," in *Proc. of FPL 2007*, 2007, pp. 796-799.

- [11] D. Alnajjar, H. Konoura, Y. Mitsuyama, H. Shimada, K. Kobayashi, H.Kanbara, H. Ochi, T. Imagawa, S. Noda, K. Wakabayashi, M. Hashimoto, T. Onoye, and H. Onodera, "Reliability-Configurable Mixed-Grained Reconfigurable Array Supporting C-To-Array Mapping and Its Radiation Testing," in *Proc. IEEE A-SSCC*, 2013, pp. 313-316.

- [12] H. Hihara, A. Iwasaki, N. Tamagawa, M. Kuribayashi, M Hashimoto, Y.Mitsuyama, H. Ochi, H. Onodera, H. Kanbara, K. Wakabayashi, M. Tada, "Novel processor architecture for onboard infrared sensors," in *Proc. of SPIE, Infrared Remote Sensing and Instrumentation XXIV*, vol. 9973, Aug. 2016, pp. 99730S-1-8.